英特尔22nm处理器全方位性能体验

3D已成为当今流行的技术元素,从15年前的《泰坦尼克》到各种显示设备,无一不在追求3D化。现在,就连英特尔新发布的22nm处理器也加入了这一行列。它由全新设计的3D晶体管打造而成,并集成了有史以来性能为强大的核芯显卡。下面,就让我们登上这艘处理器中的超级战舰,体验它那令人窒息的强大火力。

从第一代酷睿处理器到现在,英特尔带给我们一系列在性能和功耗表现上都极为优秀的处理器。随着时间发展以及Tick-Tock战略的演进,英特尔就像一台精密的机器,按部就班地向前发展。前不久,英特尔公布了自己的财报。2011年第四财季,英特尔营收高达139亿美元,净利润也达到了34亿美元之多。在2011年交出一份优秀答卷后,2012年的英特尔又会带给我们什么惊喜呢?没错,可能您已经猜到了,这就是强大的Ivy Bridge。2012年4月24日,第三代智能酷睿处理器——Ivy Bridge正式在北京发布。通过全新的HKMG 22nm 3D工艺、HD Graphics 4000核芯显卡,英特尔再次将x86处理器的技术发展水平提升到了一个新的高峰。

令人兴奋的是,Ivy Bridge处理器还拥有一个合理的价格,其高端产品的价格不超过2400元,主流产品价格大多在1300~1500元左右。显然这不仅仅是普通的新一代处理器,它更是英特尔准备用来攻占对手城池,抢占市场的利器。我们相信英特尔具备这样的实力,但更期待亲眼看到Ivy Bridge的精彩表演……

Ivy Bridge处理器技术解析

每次英特尔发布全新系列的产品,随后的评测文章中一定会提到英特尔的“Tick-Tock”发展步骤。简单来说,“Tick”就是工艺进步架构不变,“Tock”是架构升级而工艺不变。从晶体管制造发展的角度来说,“Tick-Tock”发展步骤几乎是继摩尔定律之后,又一个指导晶体管业界发展的经典规律。在这一次发布的Ivy Bridge处理器上,这个规律也得到了继续沿用。但稍有不同的是,英特尔将这款由Sandy Bridge处理器发展而来的产品定义为了“Tick+”。

“Tick”部分很好理解,英特尔将生产工艺由Sa ndy Bridge的32n m升级为22n m。依靠工艺的进步,进一步缩小了晶体管的体积、降低了芯片功耗和电压,为未来设计更强大的产品打下了基础。其次,就是引人注目的“+”部分。在小小的“+”中,英特尔带来了两项拥有重大意义的改变:1.3D晶体管首次成功应用在大规模集成电路芯片中;2.英特尔核芯显卡终于步入DirectX 11时代,赶上了桌面显卡的发展速度。此外,在CPU内核部分,Ivy Bridge虽然继承了之前Sa ndy Brid ge绝大部分的设计,但还是在模块化等设计上做出了一些改动,如采用PCI-E 3.0显卡控制器,使得显卡PCI-E带宽由PCI-E 2.0 x16的16GB/s提升到32GB/s。同时,加入Turbo Boost 2.0睿频技术,提升睿频频率,改善内存控制器,带来了同频率下CPU性能的微小增长。接下来,就让我们看看Ivy Bridge在制造工艺、规格和性能方面带来了哪些变化。

沟道——22nm的新问题

在之前的32nm时代,晶体管内部的线宽已经非常小,电子在电压驱动下运动时,很容易意外“冲出跑道”,带来诸如漏电电流和额外损耗等问题。因此英特尔很早就开发了HKMG高介电常数(金属“铪”,用于阻挡漏电电流)和金属栅极(避免栅极耗尽问题)两项技术,基本解决了栅极漏电流问题,很大程度上延续了摩尔定律。

不过好景不长,在22nm时代,进一步缩小的线宽让晶体管的源极出了问题,新出现的沟道漏电流让人头疼不已。所谓沟道漏电流,是指在晶体管越来越小的情况下,漏极越来越接近源极,栅极就越来越难以“夹断”泄漏电流,当阈值电压与沟道有严重相关性的时候,就会大幅影响晶体管的性能。这种问题在32nm时代还不过于凸显,但在22nm时代栅极越来越薄、沟道越来越短后,沟道漏电流以及随之引发的短沟道效应就成为晶体管发展的桎梏。

3D晶体管显神通

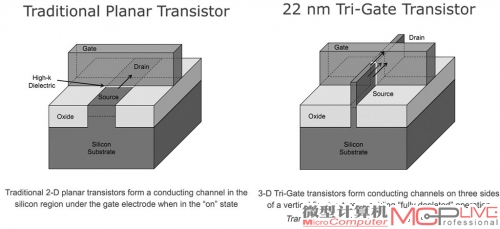

为了解决这种问题,业内的方法也是相当多样。比如台积电之前宣称22nm时代依旧会使用传统的平面晶体管,其他一些厂商如IBM和GF半导体,则考虑进一步发展SOI工艺,使用UTB-SOI技术来解决漏电等问题。英特尔显然更激进一些,早已准备好了全新的FinFET技术(Fin-Field Effect Transistor鳍状场效应晶体管)—也就是今天我们看到的“3D晶体管”。

从技术本质和生产出的产品结果来说,英特尔称呼自己的晶体管产品为“3D晶体管”有点略微“言过其实”,“3D晶体管”作为市场宣传来说,更容易让人联想到整个都立体化的晶体管产品。实际上Fin FET是晶体管制造业内广泛关注的新技术,其技术本质正如其名,使用了带了特殊“鳍”的场效应晶体管。所谓“鳍”,就是类似于鲨鱼鳍那样树立在鱼背上、有别于传统平面设计的源级和漏极。这样做可以相当大程度地避免漏电流的发生并且完美解决短沟道效应。

图左的传统晶体管只有一个电流通过方向,而3D晶体管在“鳍”的帮助下,电流可以从“鳍”的上方以及左右两侧通过,因此3D晶体管可以通过的电流更大。

如果需要一个更简单的方法来解释“3D晶体管”的话,可以认为“3D晶体管”是一种控制电流流通的特殊“阀门”。在22nm制程下,传统的老阀门已经不能很好地管理好电流了,电流的“跑冒滴漏”现象特别严重。在换用了一个新的名为Fin FET的阀门后,电流通过能力更强了,“跑冒滴漏”几乎没有了,想开就开,相关就关,整个产品的性能得到了相当明显的提升。

Ivy Bridge核心架构图,可以看出,由于采用了新一代核芯显卡,GPU部分在核心架构中占有较大面积。

虽说梦想很美好,但将一个几纳米的平面器件改成立面鳍状,其技术难度也绝对让人望而生畏。英特尔显然解决得不错。在处理器设计之初,英特尔就考虑了Fin FET技术对线路生产带来的影响,包括需要严格控制器件宽度,并将其严格量化。此外,在制造过程中,如何生产出均一稳定的“鳍”也是非常困难的,英特尔需要集中所有技术来保证这些高低交错的“鳍”的有效性和可靠性,还得保证其尽量垂直,有一定高度而且轮廓要非常鲜明。

在解决了Fin FET的技术难题后,英特尔在22nm晶体管制造上就一马平川了。很快,在实际产品中,英特尔应用Fin FET技术,并将这种工艺的效能尽可能地发挥出来。在“站立”起来的漏极和源极帮助下,以往的单个电流通道被扩大到“鳍”的左右面各一个、顶部一个(三栅极),电流流通更为顺畅,同时由于立起来的“鳍”的作用,漏电电流大大降低。根据英特尔的数据,在低电压下,Fin FET晶体管的性能提高30%,同电压下降低约50%的功耗,同时性能不变。

除了Fin FET外,之前的HKMG技术也被同时应用在晶体管制造中。这两项技术共同使用后,英特尔不但成功制造出了22nm的晶体管,同时一些关键性性能比如晶体管密度、功耗以及实际产品的面积表现都相当不错。其中,芯片的面积和成本息息相关。

在45nm的Core 2时代,四核心处理器的面积一般在300mm2左右,而在随后的32nm时代,这个数据降低到了230mm2左右。在22nm时代,英特尔又将其降低到了170mm2——其中GPU部分大约占了1/3,约50mm2;北桥部分约为20mm2;CPU核心和缓存部分约为100mm2。也就是说,英特尔目前四核心处理器的面积和之前45nm时代的双核心产品差不多,这还是在增加了大量缓存的情况下,新工艺威力可见一斑。