“干细胞”计算 创新欲统治移动多媒体

在医学领域,干细胞是一种未充分分化,尚不成熟的细胞,具有再生各种人体组织器官的潜在功能,因此被医学界称为“万用细胞”。而在IT领域,创新公司凭借Zii处理器,正试图打造以数字形态存在的“干细胞”。

在医学领域,干细胞是一种未充分分化,尚不成熟的细胞,具有再生各种人体组织器官的潜在功能,因此被医学界称为“万用细胞”。而在IT领域,创新公司凭借Zii处理器,正试图打造以数字形态存在的“干细胞”。

IBM Cell处理器开创了分布式计算新纪元,但它更广为人知的应用是索尼PS3游戏机,而IBM在过去几年似乎也未充分运用Cell。现在,创新打算接过IBM的旗帜进入分布计算时代,在年初的CES2009大展上,创新发布革命性的Zii SoC系统级芯片,该芯片具有类似干细胞的无限扩展性,创新将它称为“干细胞计算(StemCell Computing)”。

干细胞运算承载创新未来的转型梦想,凭借这一平台,创新将从音频领域跨入综合计算市场,而干细胞所具有的独特扩展性令它可以跨越从机顶盒到超级计算机这样的广阔领域,除了IBM Cell之外,还没有任何一种平台可以在架构弹性方面同它匹敌。

干细胞计算:3d Labs团队打造Zii

作为一家传统的音频厂商,创新一直给人以缓慢发展的印象,在当年的音频之战中,创新击败傲锐一统天下,并牢牢掌控了计算机音频标准。然而,板载集成声卡的出现令独立声卡陷入边缘化,市场不断萎缩,并终失去了主流用户,只停留在高端的小众化群体中。尽管创新同时也在拓展多媒体音箱等业务,但很显然它已经沦为二线厂商,这一点与图形领域的NVIDIA形成鲜明对比。

在2002年1月,创新将3Dlabs收归旗下—上个世纪末的PC玩家都知道3Dlabs的鼎鼎大名,当时它不仅拥有顶尖的工作站显卡业务,而且还进入PC显卡领域,同时3Dlabs一度掌控了OpenGL标准的主导权。不过后来3Dlabs如同Matrox公司一样,未赶上那场新世纪初的显卡大战,逐渐衰落并终被创新收购,而创新也因此获得卓越的开发技术。

创新并不打算让3Dlabs的开发人员帮助他们研发声卡,或许当时它有进入图形业的雄心壮志,可惜形势比人强,NVIDIA与ATI的疯狂战车碾碎了一切后来者的梦想,另辟蹊径是好的抉择。在这样的背景下,创新谋划了新颖的“干细胞计算”平台,3Dlabs团队就成为该项目的中坚力量。

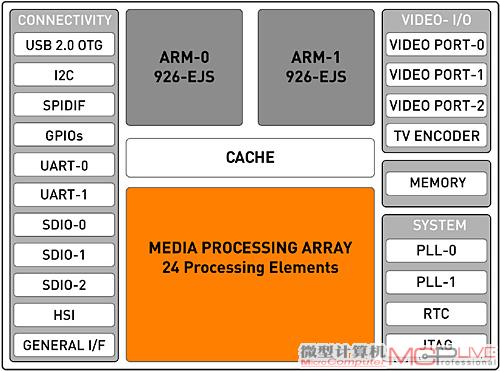

干细胞计算的基本构件就是创新的ZenII(简称为“Zii”),它其实是一颗SoC系统级芯片,型号为“ZMS-05”,集合了主控处理器、协处理器阵列、内存控制器、HDTV影像编码器以及非常强大的I/O扩展能力。ZMS芯片本身可以单独使用,也可以任意数量搭配使用,更重要的是它具有任务自适应的特点,它内部的协处理器阵列具有灵活的可编程特性,能够根据应用需要自行转变产品形态—比如说ZMS芯片在进行HDTV解码时,协处理器阵列在软件组织下自动构建为高清视频处理器的逻辑结构,但如果在任务进行中遇到3D渲染任务时,协处理器阵列中的某个部分则会变更为图形处理器逻辑,从而高效地渲染3D场景。

图1:创新Zii ZMS处理器,拥有类似干细胞的无限扩展能力是它大的特点

这种特性赋予了Zii“干细胞”平台近乎无限的可能,在面对DNA计算、宇宙探索、物理计算、

3D渲染、媒体编码等高并行度计算领域时具有出色的表现—事实上,创新率先实现了Intel的梦想,当Intel还在宣扬它的Larrabee概念之时,创新已经率先拿出了可投入商业化的“干细胞”计算平台,而“干细胞”计算所具备的无限扩展性显然是Larrabee所望尘莫及的。从这一点上讲,Intel现在多了一个可仿效的对象。而Zii被创新认为是革命性的平台也没有任何的虚夸。

ZMS处理器:干细胞计算的核心

ZMS是一款与IBM Cell(已投入实用)、Intel Larrabee(理论层面)在结构上非常相似的处理器,它们的共同点都是由数量众多的可编程协处理器单元负责运算工作,同时由一个主控CPU负责任务的指派——在Larrabee平台中,任务指派是通过外在的x86处理器完成的,而ZMS和Cell则在内部都具有CPU逻辑。在协处理器配置上,ZMS则更像Larrabee,它拥有24个处理单元(Processing

Elements,简称PE)构成的媒体处理阵列(Media Processing Array,简称MPA),比Cell的8个PE单元要多了许多。

图2:Zii ZMS处理器的逻辑架构:双ARM内核与24个PE阵列构成运算主体

1.主CPU:ARM 926-EJS负责任务指派

ZMS拥有两个ARM 926-EJS型号的CPU内核,它们的任务很明确,就是负责把计算工作分解并指派给媒体处理器阵列处理,同时它还负责控制程序的执行,“命令”处理阵列构建为相应的计算形态—比如是配置成GPU模式还是高清视频编码模式,抑或是高并行度科学计算,这些都是由两个ARM 926-EJS处理核心根据程序指令而决定的。ARM 926-EJS隶属于ARM9体系、RISC架构,ARM在智能手机、MP4等嵌入领域具有非常广泛的知名度,应用也非常普及,它的特点就是极高的能源利用效率,在完成同等计算任务下,能源消耗大概只有同类x86芯片的十分之一。ARM9架构拥有5级流水线,高频率为220MHz,指令效率达到每MHz频率1.05~1.1MIPS,ARM9内核的芯片面积小至1.1平方毫米,功耗范围则在0.85~1mW/MHz之间。换言之,ZMS中的两个ARM 926-EJS内核总功耗也不过400mW。另外在缓存、内存和指令集配置方面,ARM 926-EJ也都非常灵活,开发者可以根据需要自行调整。不过我们应该意识到,ZMS中的两个ARM 926-EJ的地位并不重要,它们仅负责一些常规的程序指令,对于整体性能的影响微小,假如创新愿意,也可以改用其它内核,当然从能效角度来看,ARM 926-EJS是目前非常理想的选择。

创新为什么选择ARM内核?

ARM公司本身并不开发实际的处理器产品,而是以IP授权的方式运作,开发者可以从ARM中购得CPU核心的IP授权,然后进行整合或者二次开发。它的客户包括Intel、IBM、德州仪器、摩托罗拉、三星半导体、飞利浦半导体、意法半导体、高通公司、科胜讯、ADI公司、安捷伦、东芝、三菱半导体等大量的半导体业巨头,ARM架构处理器几乎垄断了智能手机及其它嵌入式平台市场,而创新公司也是其中的一员。

作为对比,我们来看看IBM的Cell与Intel还在纸面上的Larrabee。Cell中也拥有一个功能类似的主CPU单元,它采用的IBM PowerPC 970架构,除了指令架构与性能不同外,它与创新ZMS在功能上完全相同,都是负责任务的分配与指派,不负责实际计算工作。Intel的Lar rabee中则不具备这个单元,任务指派是由x86处理器来完成的,这也决定了Larrabee只能针对PC到超级计算机的领域,而无法用于嵌入场合。

2.媒体处理阵列:性能与任务弹性的关键

ZMS的真正核心是由24个PE处理单元组成的计算阵列,这24个单元被平均分为3组,它采用的是高密集计算的SIMD流处理架构,即类似于Intel Larrabee中的协处理器和AMD Radeon HD 4000中的流处理器(NVIDIA GPU采用的是MIMD架构,Multiple Instruction Multiple Data,多指令多数据流)。SIMD是CPU中的一个基本概念,它是指单指令多数据流(Single Instruction Multiple Data)技术,也就是CPU可以用一条指令同时处理多个操作数,SIMD虽然在分支预测时会遇到效率较低的问题,但在密集浮点计算应用中SIMD架构的效率优势则十分明显。PE单元包括整数、16-bit浮点和

32-bit浮点处理单元,可以高效地完成整数和浮点计算工作。

在实际应用中,ZMS对PE单元的分配是以组为单位进行的,也就是每8个PE单元构成的阵列作为基本的计算单位,这三组PE阵列可以共同完成一个任务,也可以各行其道。比如可以将两组PE阵列构建为3D渲染模式,1组PE阵列则为高清视频处理模式,具体采用何种模式是由任务本身自行决定的。而且,PE阵列可支持空闲任务切换机制,当某组PE阵列处于空闲状态时,系统可以将其他任务部署到该阵列上,实现资源利用的佳化。另外,PE阵列支持独立的频率控制机制,如果没有额外的任务分配,该组PE单元的工作频率可以自动降低以实现节能。

图3:24个PE阵列可根据任务要求自动配置,从而实现高效率的密集计算

24个PE单元共同分享高速缓存与系统的内存资源,但每一个PE单元都可以独立地访问缓存或内存,这就赋予了PE很强的灵活性—ZMS处理器具有166/266MHz的32位或64位内存总线,支持

Mobile SDR、DDR和DDR2内存规范,但尚未支持DDR3,这样的规格看似有些落后,不过我们要考虑到Zii平台主要的应用还是嵌入式应用,这类设备并不需要非常海量和快速的内存系统,对于功耗的要求则比较注重。在这方面,ZMS处理器同样比较完善,它的内存总线可以根据系统负载弹性调整,在闲置状态时自动降低能耗和时钟频率以实现节能。PE阵列对于存储资源的访问则是以“组”进行的,这一点不难理解,因为由8个PE组成的小阵列就是ZMS的小任务单位。

在24个PE单元的共同努力下,ZMS处理器高可以提供10.15GFlops和32Gops(十亿操作每秒)的性能,作为媒体解码器时可胜任30帧/秒、8Mbps的MPEG-4/H.264格式720p视频流,作为

GPU时可提供42M pixels/s像素渲染、21M ver t ices/s顶点渲染的性能,图形API则是基于针对嵌入软件的OpenGL ES 1.1和2.0。也许大家会不自觉地把它与NVIDIA或AMD的顶级GPU对比,并发现其性能数据非常寒碜,不过这样的对比并没有意义,因为ZMS的首要应用主要是智能手机等要求低耗能的手持设备。对这些设备来说,Zii平台所提供的10.15GFlops计算能力已富足有余。另外,Zii的关键特点是具有无限扩展性,创新表示,Zii可以在A4纸大小的空间里组成一台TFlops级别超级计算机,在576个刀片服务器里安装147456颗ZMS处理器后就能达到PFlops级别,与当今性能强的

IBM Roadrunner相差无几。由于这种特性与“干细胞”非常类似,所以创新也据此提出“干细胞计算(StemCellComputing)”新概念。

图4:Zii ZMS处理器尺寸极小,A4大小的空间内可组成TFlops级别计算机

在实际应用中,ZMS的PE阵列可以根据程序需要自我重新编程,除了作为GPU和高并行度流计算处理器外,它还可以组织为高清晰音频、高质量图像引擎(比如用于数码相机的图片处理),灵活变换各种不同的组态,同时可以根据负载需要开启或关闭部分PE核心,这些特性令Zi i平台具有极佳的任务延展性,创新表示,Zii面向的市场非常广阔,小到智能手机、手持设备、GPS导航仪、机顶盒、媒体播放机,大到从事流媒体计算的超级计算机,Zii都可以游刃有余。

3.ZMS所集成的功能

作为一枚SoC级芯片,ZMS本身就具备完整的扩展功能,但它远比我们想象得要强大。首先,ZMS芯片内直接集成了1080p级的高清电视调谐器,可支持NTSC、PAL和SECAM等多种制式,这意味着ZMS芯片可以为相关设备提供数字电视播放能力,配合24个PE阵列的处理能力,数字电视厂商只要使用一枚芯片就能够满足基本的播放要求,使用两枚芯片则可以满足图像处理优化的高级需要,这样的结构显然要比传统的CPU+HDTV处理芯片的构成要简洁,而且也具有更好的扩展性。

图5:Zii平台的应用领域广泛,智能手机、数码相机/摄录机、机顶盒等嵌入领域是它主要的市场

在影像输出方面,ZMS拥有三个双向的独立视频流通道,可满足LCD显示设备、数字图像传感器(CCD或CMOS)、影像编解码设备的输出和输入要求—当ZMS与CCD/CMOS连接时,它实际上扮演了图像处理器的角色,可以集成于高阶数码相机或数码单反产品中,而采用ZMS方案无疑要比自行设计图像处理芯片来得简单,厂商不再需要理会硬件因素、只要根据ZMS的SDK编制好相应的图像处理程序即可。

ZMS的I/O接口还包括USB 2.0、三个独立的SDIO/MMC移动存储接口、SPDIF光纤接口和32-bit可编程的通用传输总线,这条通用总线可以被配置为ZMS芯片间直连或其他Zii ZMS设备的直连,或者配置为以太网接口、IDE接口等等,OEM厂商有足够大的自由度进行灵活选择。不难看出,Zii

ZMS其实就是一部芯片级计算机,OEM厂商只要为它配置内存和必要的I/O连接,就完成了硬件部分的设计、显得快捷简单。

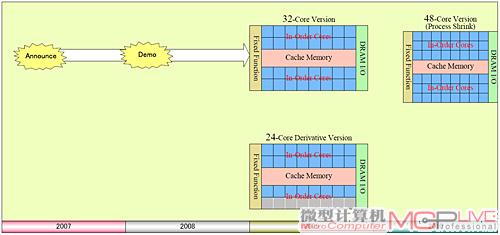

Zii轶事

Zii出自3Dlabs团队之手,这一点确信无疑,不过3Dlabs的开发者并不是从零开始打造Zii,Zii的形成经历了两代演化。早在2004年,3Dlabs即计划从创新中剥离为一家独立的无工厂芯片设计公司、并打算更名为3Dlabs半导体(3Dlabs Semiconductor),主打数字媒体处理芯片。同时它们推出了一款型号为DMS-02的媒体芯片,它基于ARM多核架构,内建了两个ARM 926EJ核心,多级缓存,3个双向视频流端口,32或者64-bit移动内存,大1.6GBps带宽,与连接LCD、CMOS传感器,IDE 硬盘,USB OTG,闪存和Audio DAC多种设备连接。DMS-02可以执行视频、音频、2D/

3D图形处理,以及GPS、radio、DMB数字广播等多种处理任务—在当时,DMS-02的性能指标非常强悍,它的计算能力达到4.8GFLOPS,可支持H.264 720p视频回放、且此时芯片的功耗低于1W,同时3D导航功能上的渲染帧数达到30fps。

图6:3Dlabs早年开发的DMS-02媒体处理器,Zii ZMS即在它的基础上构建

从这些指标中我们不难看出,DMS-02与今天的Zii ZMS处理器拥有惊人的相似性,后者显然是在前者基础上扩展了PE计算阵列,同时实现了无线扩展以及可编程的任务自适应。3Dlabs的DMS-

02并没有获得广泛的成功,它似乎也没有如期从创新中拆分,在随后的几年间,3Dlabs的员工们显然开始以DMS-02为基础秘密开发了Zii,而Zii的开发耗费了创新十亿美金。当然,Zii ZMS与昔日的DMS-02也不可同日而语,除了同样针对嵌入领域和基于ARM架构外,两者的设计思想迥然不同。

在发布Zii的同时,3Dlabs悄然改称为ZiiLabs实验室,假如你访问www.3dlabs.com网站就会发现这一点。现在,3Dlabs决意与自己的光荣传统告别并轻装上阵,Zii也将成为3Dlabs和作为母公司的创新未来十年重要的“战略武器”。

软件支持:“干细胞”与Cell、Larrabee的异同

基于结构上的相似性,大家把Zii与Cell、Larrabee拿来相提并论是情理中事,这三者在设计思想方面的确存在相当多的共同点:主处理单元只负责任务指派,实际计算工作都是通过数量较多的PE协处理单元完成,PE协处理器都采用流计算优化的SIMD架构。但这三者仍然有自己鲜明的特点:Zii具有独特的无限扩展性、任务自适应性和低功耗特征,它主要针对嵌入式应用,智能手机、手持设备、机顶盒等是它重要的应用;Intel Larrabee专注于图形渲染和高并行运算,Intel同时推行自己的x86扩展指令集;Cell目前主要应用在索尼PS3游戏机以及松下数字电视产品中,在高性能视频处理应用中表现卓越,而在超级计算机系统中,Cell则以协处理器的面目出现专注于高密集浮点运算。

图7:Cell处理器拥有8个协处理器,程序编制难度大限制了它的应用

在发布Zii的同时,创新也公布了Zii平台的开发工具。事实上,对这类拥有数量众多内核的处理器来说,如何有效地编程是其中的难点。Zii ZMS中的PE阵列以何种组态存在,完全取决于程序本身—假如程序足够优化,那么的确能够发挥出Zii任务自适应的优势;但如果程序编制得糟糕,那么

Zii平台将表现出低下的效率。

正因为如此,Zii平台对于程序的编制水准高度依赖,这也是创新在未来要面对的关键问题。不过对创新来讲,应用软件的问题并非瓶颈所在,因为创新公司将承担Zii实用化的先锋,得益于之前DMS-02媒体处理器的开发经验,创新可以很快地将Zii ZMS芯片用于自己新的媒体播放器产品中,同时创新也有能力拿出相应的软件平台,包括嵌入Linux和多媒体处理软件—在Zii的官方网页中,我们已经看到Google Android操作系统可以在Zii平台中顺利运行,这也意味着Zii进入智能手机市场完全没有障碍。此外,创新也发布了相应的中间件,借助这个中间件OEM厂商可以开发出Zii优化的应用。

与Zii形成鲜明对比,IBM Cell和Intel Larrabee都受制于软件的支持。首先我们来看Cell平台,它的PE协处理器虽然只有8个,但是性能更为强大,同时Cell具有高达4GHz的高频率足以保证了惊人的浮点性能。Cell可以支持分布式运算机制,即任务可以被分布于整个Cell网络的其他处理器中—这种特性与创新“干细胞”其实如出一辙,只是IBM没有作此宣传而已。Cell的PE协处理器同样具有高度可编程特性,问题在于IBM只是作为平台供应商,应用软件则由Cell的使用者开发。

图8:Intel Larrabee与Zii非常类似,都是采用数量较多

的协处理器单元,但Larrabee目前还是纸面上的产品

索尼初在设计PS3中曾雄心勃勃,打算用Cell来渲染3D图形,不过索尼很显然为如何有效编程困扰,而IBM当时没有公布完善的中间件,索尼终不得不放弃Cell渲染的计划,转而选择传统的NVIDIA GPU方案。目前除了PS3之外,Cell还被东芝用于液晶电视机和笔记本电脑中、负责对视频进行处理,这也是Cell目前较为成熟的应用。

Intel的Larrabee同样将面临软件支持的问题。Intel为Larrabee平台带来全新的指令集,尽管该指令集在x86基础上扩展,开发人员容易入手,同时也很具弹性,比如说它既可以执行高密集计算也可用于3D渲染。但问题就在于Larrabee的一切还是未知数,Intel很难说服开发者在不知道其性能高低的情况下就花费高昂的精力为它编程,大概没有一个游戏开发者愿意这么干,毕竟对于3D渲染来讲,微软DirectX和OpenGL都是更为成熟的选择;而对于密集的流计算,NVIDIA的CUDA平台也更为成熟。

障碍:如何击败传统势力?现在已经有足够多的解决方案

尽管Zii处理器的小体积、超低功耗和无限扩展性让它能够在A4大小空间实现TFlops级别计算能力,或在576个刀片服务器里安装147456颗Zii处理器达到PFlops级别性能,但指望Zii进入超级计算领域显然是不务实的,原因并非在于性能的限制—其中关键的障碍在于创新在超级计算领域并无根基,现在Intel、IBM、AMD、NVIDIA都已经提供了足够多的方案,创新也很难说服超级计算机厂商选择Zii来构建超级计算平台。

对于这一点创新心知肚明,为此将Zii定位于自身所擅长的嵌入领域,集合自身在多媒体技术的优势,打造出一套面向未来的梦幻级嵌入式平台。对于这一点我们毫不怀疑,很快我们就会首先在创新的产品中看到Zii,只要它的表现足够出色,那么将能够不断吸引其他厂商的参与。我们同样不怀疑分布式计算是IT工业的未来方向所在,在它所专注的领域,Zii并没有强有力的对手。创新对Zii则寄以厚望,它急于摆脱“声卡之王”的讥讽,转身成为重量级的数字媒体供应商,而Zi i和“干细胞计算”也许真能够帮助创新做到这一点。